| 您现在的位置: 首页 > 新闻动态 > 图片新闻 |

| 核高基重大专项“嵌入式可编程逻辑阵列IP核”课题顺利通过验收 | ||||||||||

|

||||||||||

|

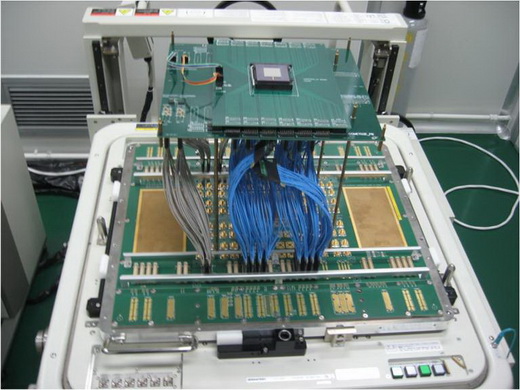

ATE测试平台

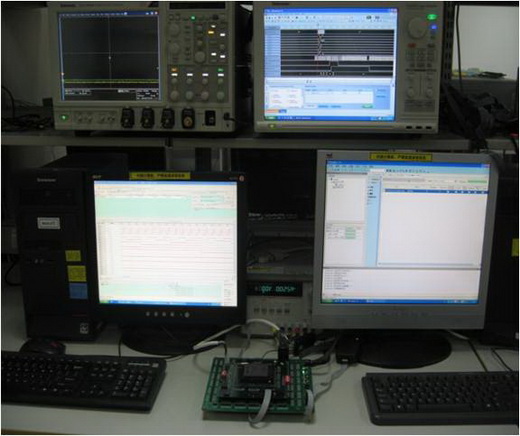

板级测试平台

专家现场验收 2012年11月21日,核高基重大专项“嵌入式可编程逻辑阵列IP核”课题验收会在北京召开。该课题由中科院电子所牵头,联合中科院微电子所和中芯国际集成电路制造(上海)有限公司(SMIC)共同承担。 工业和信息化部电子信息司任爱光处长,核高基专项实施管理办公室、北京市经济和信息化委员会科技处等单位的相关领导出席了验收会,电子所所长吴一戎院士到会致辞。 来自浙江大学、中国半导体协会、工信部软件和集成电路促进中心、电子科技大学、安徽大学、中电集团公司、中科院声学所、半导体所等多个单位的专家组成的课题任务验收组,认真听取了项目负责人中科院电子所可编程芯片与系统研究室主任杨海钢研究员所做的课题总结汇报。工信部电子工业标准化研究所和工信部软件与集成电路促进中心(CSIP)分别就芯片测试和试验情况作了第三方评测报告。电子所航空微波遥感系统部秦于华副研究员也针对基于嵌入可编程逻辑阵列IP核SoC芯片的机载雷达成像系统应用作了验证示例。验收专家组认真审查了项目技术材料,第三方测试报告、实验数据以及经费审查报告,观看了现场系统演示,查验现场测试数据,并考察了课题人才培养和团队建设情况,认为课题完成了合同规定的任务,各项指标均达到任务书立项指标,一致同意通过验收。 “嵌入式可编程逻辑阵列IP核”课题面向国家高技术战略发展需求,成功完成了重大专项课题任务书规定的全部任务,研制出“慧芯一号增强版”IP核产品,同时自主开发了相应的软件设计系统,在嵌入式IP核软硬件全正向设计关键技术上取得了全新的阶段性重大突破,申请了多项发明专利,并在国家重点工程雷达数据加密系统中得到实际工程应用验证。同时,课题还充分利用了联合单位中芯国际在集成电路制造工艺、器件建模、电路设计套件和标准单元库等基础IP开发方面的经验,为嵌入式可编程逻辑阵列IP核的开发提供工艺技术和设计环境支持,并尝试借助中芯国际半导体代工的商业模式,推动嵌入式可编程逻辑阵列IP核的市场化与商业应用。 通过项目的实施,电子所在研制条件保障平台和人才队伍建设上都取得了跨越式的发展,目前已形成了一支具备芯片设计、可靠性加固、软件开发、器件测试、应用开发等多方面能力的综合性人才创新团队。 该课题的顺利验收,标志着我国在研制具有自主知识产权的高性能大规模嵌入式可编程逻辑阵列IP核能力上的创新突破和显著提升,是国产可编程逻辑芯片和IP核在探索市场化和产业化道路上的重要里程碑,对我国抢占集成电路新兴产业战略制高点有着重要的意义。 |

||||||||||

| 评 论 |

| 相关新闻 |