| 您现在的位置: 首页 > 新闻动态 > 综合新闻 |

| 电子所大规模FPGA布局算法优化新进展亮相第十三届可编程技术国际会议(ICFPT) | ||||||||||

|

||||||||||

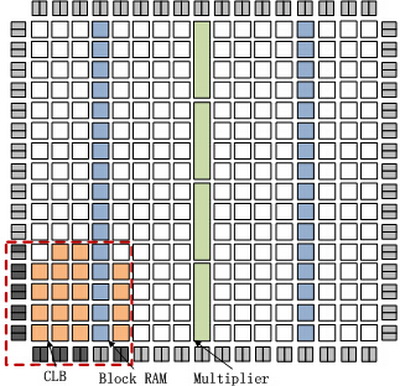

| 第十三届可编程技术国际会议于2014年12月10日至12日在上海举行,这是可编程技术和可重构器件与计算系统领域最知名的国际会议之一。杨海钢研究员带领的可编程芯片与系统研究室团队的论文 “Size Aware Placement for Island Style FPGAs”作为口头报告被大会收录,论文作者之一、博士研究生黄俊英代表参会。本次会议共收到来自23个国家的121篇论文投稿。在121篇论文投稿中,经会议技术程序委员会筛选,其中23篇录用口头报告(录用率为19%),24篇录用海报报告。 本次可编程技术国际会议为期三天。主题报告均来自相关领域著名的公司和大学,包括Synopsys、Microsoft和UCLA。演讲报告分7个主题讨论会,共34场,覆盖可编程芯片软件工具和设计生产率、金融应用、可编程芯片结构和实时系统、数学电路、硬件安全、应用和器件、工业界专场七个主题方向。在可编程芯片软件工具和设计生产效率方面,3个主题是在高层综合领域的研究,2个演讲报告为与FPGA布局算法相关的研究。随着FPGA在金融领域应用的深入,大会将金融应用作为单独主题讨论会,设有4个演讲报告。在可编程芯片结构和实时系统方面,包括组粒度可重构结构处理单元、结构综合、异质系统的存储器访存、FPGA软核处理器4个报告。数字电路演讲报告,对FPGA的浮点除法、数字并行算术操作符的高效FPGA实现、QR分解的高效FPGA实现、优化面积的浮点加法器和乘法器、基于FPGA的浮点矩阵处理器分别进行了讨论。 随着FPGA芯片的集成度和复杂性的增加,开发快速高效的FPGA计算机辅助设计(CAD)算法是研究的一个热点。在FPGA的CAD编译流中,布局布线非常重要,因为它们不仅占用了大部分的编译时间,而且直接影响了电路的工作频率。传统的改进FPGA布局布线质量和运行时间的方法可以分为两种:基于软件和基于硬件的方法。基于软件的方法通过改进模拟退火算法的多个方面,比如较优的初始布局、定向移动代替随机移动、有效的退火表、多级策略等。此外,解析布局也得到了广泛的研究。FPGA布线算法基于迭代的机制,比如协商拥挤策略、改进的PathFinder布线算法、时序约束的布线算法等。基于硬件的方法需要更多的硬件实现逻辑块的交换和信号的布线。但是,以上的研究在FPGA布局布线时都未完全考虑日益增大的芯片尺寸。 本文首先探索FPGA的尺寸对布局布线的质量和运行时间的影响。实验结果表明,采用规模较小的FPGA芯片实现电路,能获得较好的性能和较短的布局布线运行时间。当芯片的面积增大100倍时,布线后的线长增加103%,布线后的关键路径延时增加13%,布局运行时间增加285%,布线运行时间增加15倍。 为了解决使用规模FPGA芯片实现电路带来的性能下降和运行时间过长的问题,文中提出Min-Size布局算法。该算法把逻辑块和IO约束在一个阵列区域内,IO被约束在这个阵列区域的左下角,逻辑块则被约束在区域的中心,如图2所示。此外,为了减小布局布线的运行时间,Min-Size算法只建立与这个阵列区域对应的延时矩阵和布线资源图。

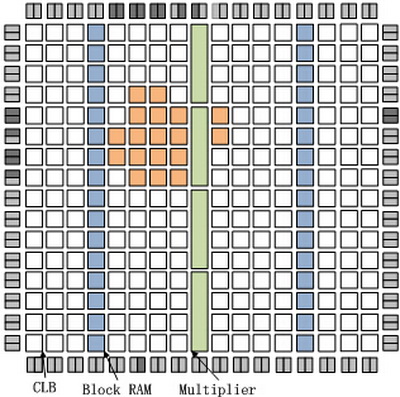

图1 传统的VPR布局算法示意图

图2 Min-Size布局算法示意图

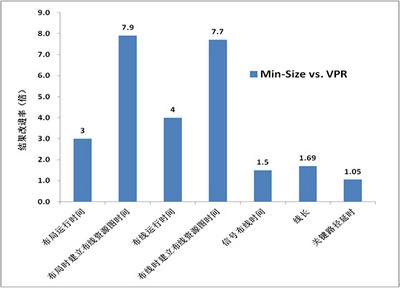

为了评估Min-Size布局算法,文中采用实验的方法与VPR(学术界广泛研究的布局布线工具)进行比较。如图3所示,当FPGA芯片尺寸增大10倍时,与VPR相比,Min-Size算法中布局运行时间、建立布线资源图时间和计算延时矩阵的时间分别加速了3倍、7.9倍和106倍;布线运行时间、建立布线资源图时间和信号布线的时间分别加速了4倍、7.7倍和1.5倍;布线后的线长减少41%,关键路径延时减少5%。研究同时表明,由于该算法的布局布线时间不受芯片尺寸的影响,只与被实现的应用电路规模有关,因此,当FPGA芯片规模更大时,Min-Size算法的布局布线时间会有更多的改进。 (十一室 尹韬)

图3 Min-Size与VPR的运行时间和性能比较 |

||||||||||

| 评 论 |

| 相关新闻 |