|

深亚微米集成电路单粒子翻转加固设计技术取得突破性进展,相关成果发表于IEEE TNS期刊 近日,电子所杨海钢研究员带领的可编程芯片与系统研究室团队在深亚微米集成电路单粒子翻转加固设计技术领域取得突破性进展,提出了一种新颖的三互锁(TILL)结构锁存器,经试验表明,比已沿用20多年的传统双互锁(DICE)结构锁存器在抗单粒子及综合“延迟-面积-软错误率”性能指标上提高1个数量级。基于该成果,该团队的博士研究生李天文和其导师杨海钢研究员及其他3名研发人员在抗辐照技术顶级SCI期刊IEEE Transactions on Nuclear Science(Vol.61, No.6, December 2014)发表了论文《A CMOS Triple Inter-Locked Latch for SEU Insensitivity Design》。 当芯片应用于空间环境中时,各种宇宙射线、粒子可能会击中并穿过电路,其径迹上发生电离而产生电子-空穴对,这些电子-空穴对被电路的节点吸收后,会造成时序电路和存储电路数据错误,导致电子系统功能异常甚至失效,这种效应称为单粒子翻转(Single Event Upset, SEU)。随着集成电路制造工艺节点不断减小,电路更容易受到空间辐射影响。锁存器是大规模集成电路中的关键时序单元,对空间单粒子效应尤其敏感,提高其抗单粒子翻转性能对整体电路的抗辐照性能至关重要。 抗辐照加固方法可分为特殊工艺和电路设计加固两类,工艺加固是采用特殊的芯片生产工艺线,减小器件对电子-空穴对的收集。但特殊工艺线生产流程较复杂,且往往落后商用工艺,降低了芯片集成度。因此,电路设计实现抗辐照的方法得到了快速发展。目前常用的锁存器设计加固方法有三模冗余、软错误缓解 (Soft Error Masking, SEM)、施密特结构 (Schmitt Trigger, ST)、双互锁(Dual Inter-locked Cell,DICE)技术等。三模冗余技术通过多数判决机制来消除单个翻转错误,但并不能提高基本单元的翻转阈值,且增大了面积和功耗,降低了速度,从而限制了其在大规模集成电路中的应用。SEM与ST结构在普通锁存器的基础上进行改进,增大节点电容与反馈通路延时,虽然提高了电路节点抵抗翻转的能力,但降低了电路性能。DICE结构中当两个节点同时出现翻转时,仍会发生功能错误。 博士研究生李天文在其导师杨海钢研究员指导下,通过长期深入的研究,不断设计优化实验,研发出一种新颖的三互锁结构锁存器(Triple Inter-Locked Latch, TILL),如图1所示。该结构电路对多节点出现的单粒子翻转免疫,与其它几种传统单粒子翻转加固锁存器的性能比较,三互锁结构速度提高24%,功耗延时积较小22%,面积仅增大17%。且与其它结构的单粒子翻转加固效率,即模块的软错误率/(面积*延时功耗积),对比分析显示,三互锁结构具有最高的加固效率,如图2所示。

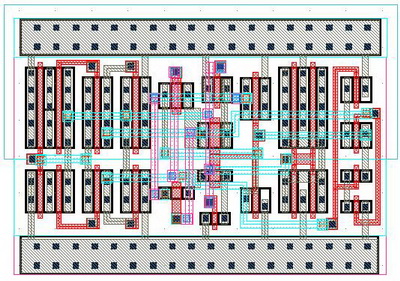

图 1三互锁结构(TILL)加固锁存器

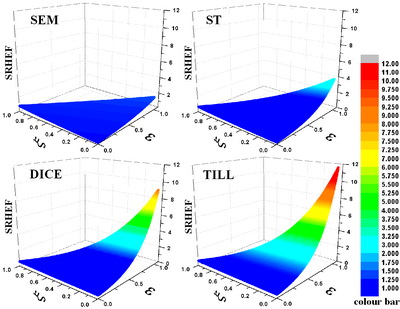

图 2 TILL与其它结构的单粒子翻转加固效率比较

测试芯片采用先进的标准CMOS工艺设计实现,该芯片的单粒子辐照试验检测系统与辐照环境如图3所示。辐照试验得出的翻转截面比较结果如图4所示,三互锁加固结构的单粒子翻转阈值大于42MeV-cm2/mg, 其翻转截面比传统加固结构低至少一个数量级。 目前该研究成果已在研究室最新芯片产品中得到应用,以进一步提升国产“慧芯”系列芯片的空间应用可靠性和抗辐照能力。(十一室 黄志洪)

|